The clock counts and assigns the numbers and it's position. The outputs are the anodes and the digit.

The numbers after "D" refer to the decimal place on the 7 segment display.

#PONG GAME CODE IN VHDL DRIVER#

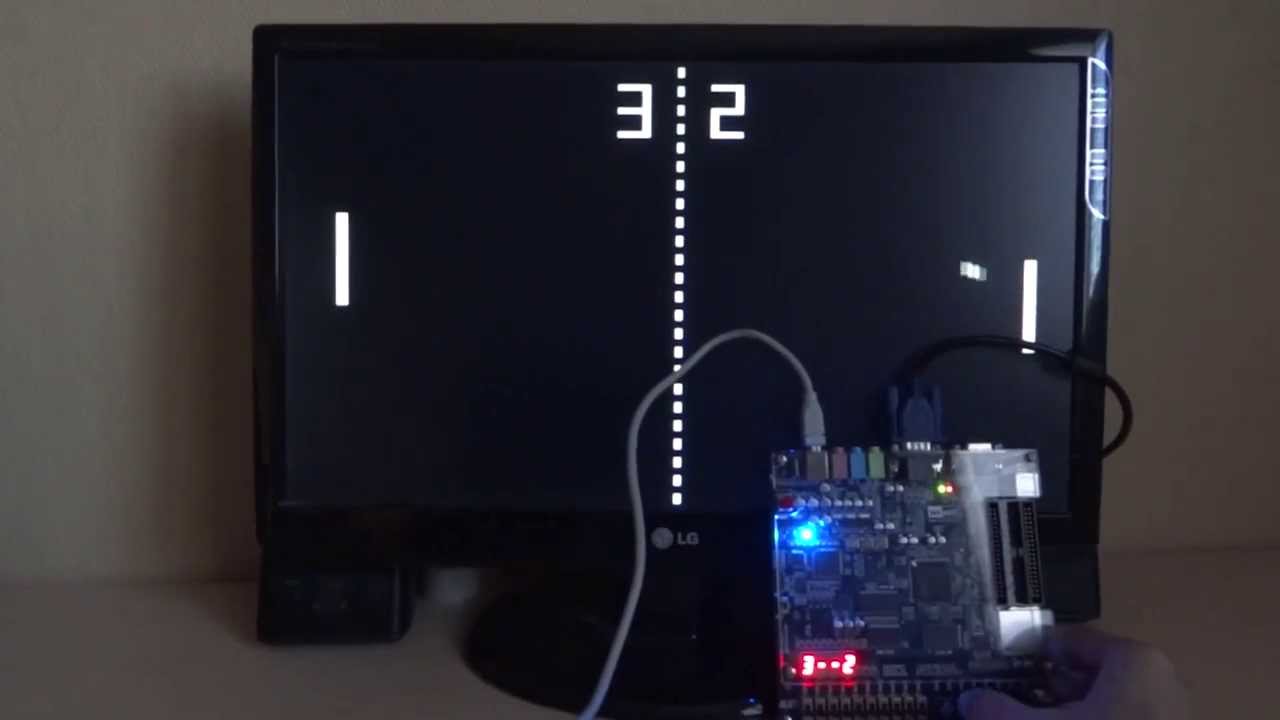

The segment driver has inputs D1, D10, D100, D1000, and Clock. The score counter has inputs Clk(Clock) and RST(Reset) and outputs Clk_Out and Q which essentially acts as the score output. If the enable signal is on, then the clock will count on the rising edge. The clock divider has inputs Clk(clock), CEN(enable in), and Div(divider) and output Clk_out. The code for all five files is attached below. The score handler puts together all the pieces and maps the signals. It includes a clock divider that is used to count the seconds, a score counter counts the seconds that the user is playing, the segment driver take the score and converts it to anodes and cathodes to be displayed on the screen and also determines the position that the number will be displayed and lastly, the segment handler converts the binary digits to decimal digits to be displayed on the screen. This section consists of files that relate to displaying the score in seconds on the 7 Segment Display on the Basys3 Board. The button logic module will also consist of a clock divider, and a programmable memory, as well as a binary to decimal converter for the 7-Segment Display with its respective clock divider. The VGA Driver will consist of programmable memory, a clock divider, and the logic that will manipulate the output for color. The two main submodules are the VGA Driver, as well as the button logic module. This project has two main modules and an array of submodules that will manipulate the input data. We will be using a few counters, one to refresh the display and one to count up the score as you continue to play. We will have the control input of the DeMux be present state of the sub-FSM so that we can control how fast the game will go by how long that you play it. The game will move much faster the longer you play. Our gizmo will also use at least three clock dividers, one for the score (time), one for the refresh rate of the of the display and one that is hooked up to the output of a DeMux so that we can control how fast the game will proceed with increasing amounts of difficulty. The number will be displayed as a decimal number.Ĭircuit Architecture: We will build our gizmo using one FSM that contains a smaller FSM, the sub-FSM will control the difficulty of the game whereas the main FSM will control the overall flow of the game. The 7-Segment Display will be used to record the score, which is the number of seconds that the user has been playing without losing the game. It has a horizontal and vertical sync outputs, RBG(which refers to the color of the pixel at a certain location), and Score(which acts as a bus to the 7-Segment display).The up button will be used as the start button, and the left and right pushbuttons will be used to move the paddle in their respective directions. The system has four inputs: Button R, Button L, Start, and Reset, and a Clock. The diagram below is the basic overall top-level block diagram for the system. The levels are determined by the speed of the ball this means that every ten seconds, the speed of the ball increases, thus increasing the difficulty of the game. There are five levels, and every ten seconds the level increases, until you hit level 5 where it stays till the user loses. The time of the run will be recorded on a 7 segment display. In order to reset the game, the user must push the center button. The user will be able to use the left and right pushbuttons to determine the movement of the paddle. The game is over when the ball fails to hit the paddle. If the ball hits the paddle, it bounces up again and continues to bounce until it misses the paddle. When the user presses the start button, which is the up button, the ball will begin bounce up, and will bounce off the wall and attempt to hit the paddle. The game consists of a display with a sliding paddle that can be controlled by the user, and a fixed wall that acts as the upper bound. The Image above is the overall schematic design of the project.

0 kommentar(er)

0 kommentar(er)